¶ TF card

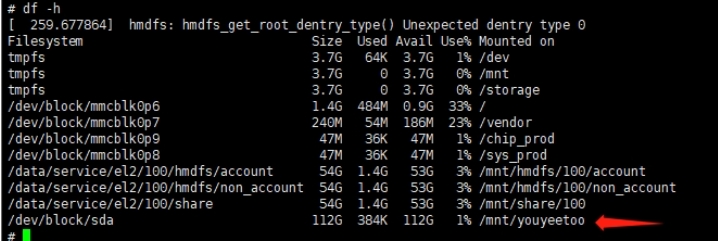

From the schematic, it can be seen that the TF card slot of yy3568 is hung on SDMMC0.

###TF card device tree

- Clock frequency: 150000000

- Line width: using 4-wire SDIO

- Set up support for SD cards

&sdmmc0 {

max-frequency = <150000000>;

supports-sd;

bus-width = <4>;

cap-mmc-highspeed;

cap-sd-highspeed;

disable-wp;

sd-uhs-sdr104;

vmmc-supply = <&vcc3v3_sd>;

vqmmc-supply = <&vccio_sd>;

pinctrl-names = "default";

pinctrl-0 = <&sdmmc0_bus4 &sdmmc0_clk &sdmmc0_cmd &sdmmc0_det>;

status = "okay";

};

¶ Verification testing

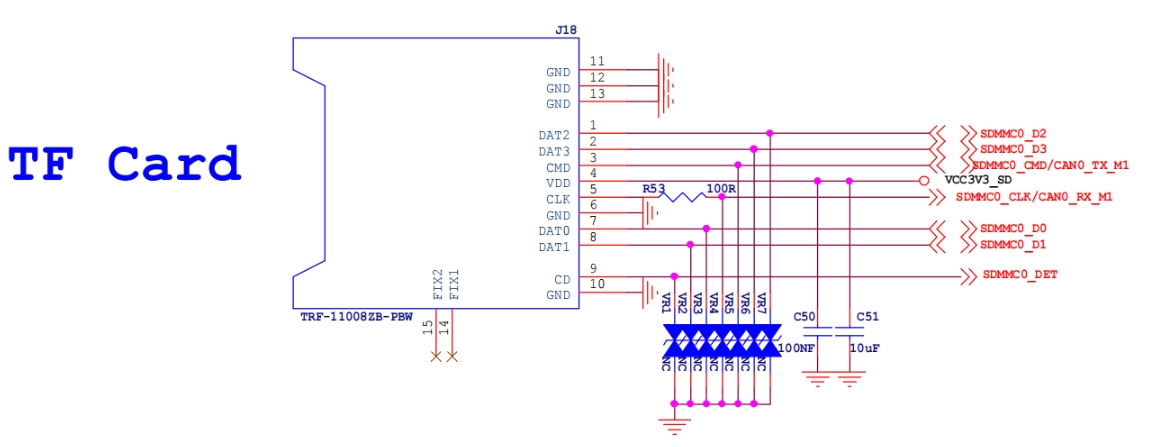

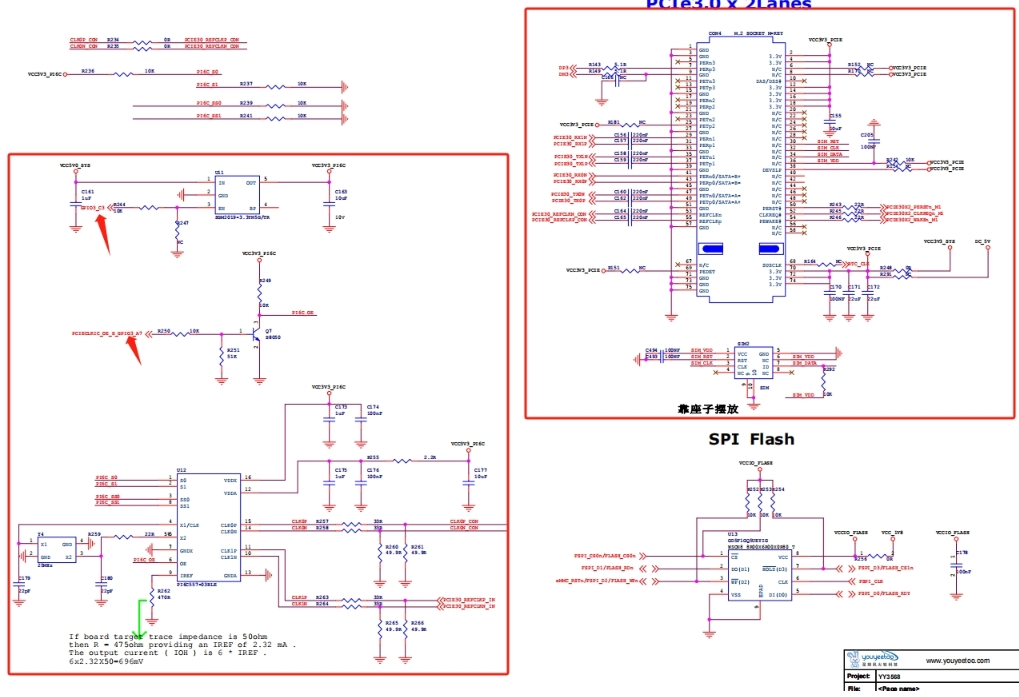

- We will add a file in the TF card: youyeetoo.txt, for us to verify on yy3568:

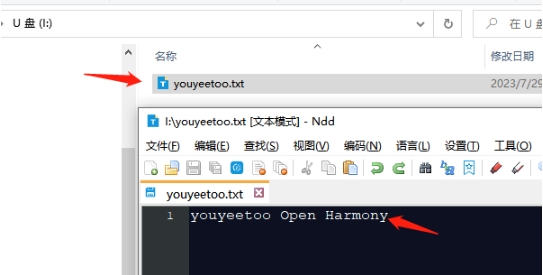

- Compile and burn, insert the TF card onto the board, and the serial terminal can view the TF card information. The block device name is mmcblk1p1 and the size is 117GiB.

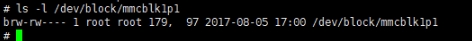

- You can see the device file mmcblk1p1 of the TF card under/dev/block.

- Mount the TF card and verify if it is mounted successfully. The operation command is as follows:

- View TF card device files:

ls -l /dev/block/mmcblk1p1

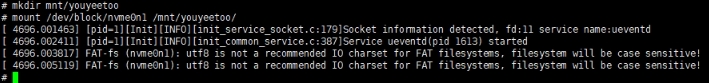

- Create a file called youyetoo under/mnt/for TF card mounting:

mkdir /mnt/youyeetoo

- Mount TF card to/mnt/youyetoo:

mount /dev/block/mmcblk1p1 /mnt/youyeetoo/

- Check if the mounting is successful:

ls -l /mnt/youyeetoo/

- Verify the contents of the TF card:

cat /mnt/youyeetoo/youyeetoo.txt

¶ SSD

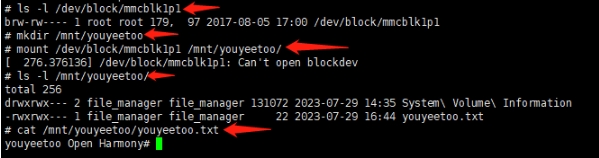

From the schematic diagram, it can be seen that the SSD of yy3568 is plugged into PCIE3.0 and has two pins that need to be controlled: the power pin GPO3_C3 and the clock enable pin PCIECLKIC-OE_H_GPO3_S7.

¶ SSD device tree

Power Pin Device Tree Configuration

vcc3v3_pcie: vcc3v3-pcie-regulator {

compatible = "regulator-fixed";

regulator-name = "vcc3v3_pcie";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

enable-active-high;

gpio = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&pcie30_pwr>;

startup-delay-us = <5000>;

vin-supply = <&vcc5v0_sys>;

};

Clock enabled pin device tree configuration

pcie-oe-regulator {

compatible = "regulator-fixed";

gpio = <&gpio3 RK_PA7 GPIO_ACTIVE_HIGH>;

pinctrl-names = "default";

pinctrl-0 = <&pcie_oe>;

regulator-name = "pcie_oe";

//enable-active-high; //active low

regulator-always-on;

regulator-boot-on;

};

PCIE interface enable

&pcie3x2 {

reset-gpios = <&gpio2 RK_PD6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie>;

pinctrl-names = "default";

pinctrl-0 = <&pcie30x2m1_pins>;

status = "okay";

};

¶ Verification testing

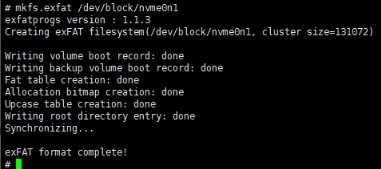

- Format SSD, command: mkfs.xfat/dev/block/nvme0n1

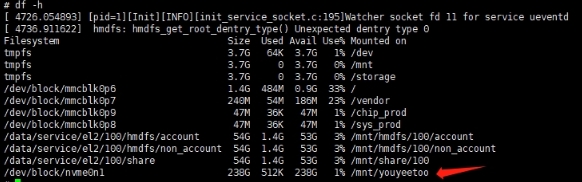

- Mount SSD devices

mkdir /mnt/youyeetoo

mount /dev/block/nvme0n1 /mnt/youyeetoo

- Check if the mounting is successful

¶ SATA

The WiFi interface and SATA interface of YY3568 use the same M.2. WiFi and SATA cannot be used simultaneously

¶ SATA device tree

Phy device tree

&combphy2_psq {

status = "okay";

};

Sata device tree

&sata2 {

status = "okay";

};

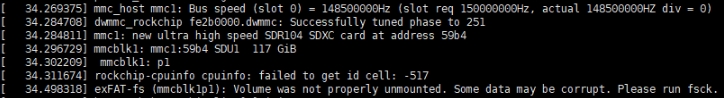

¶ Verification testing

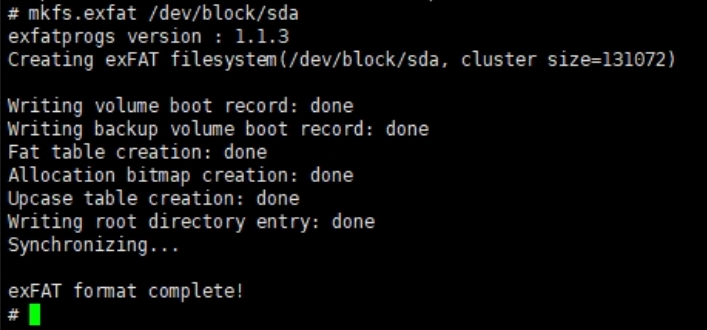

- Format SSD, command: mkfs.xfat/dev/block/sda

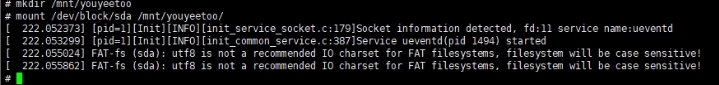

- Mount SSD devices

mkdir /mnt/youyeetoo

mount /dev/block/sda /mnt/youyeetoo

- Check if the mounting is successful